# Imagination Developers Connection

## PowerVR Graphics Keynote

**Rys Sommefeldt**

## **PowerVR Rogue Hardware**

# **PowerVR Rogue Recap**

Optional secondary message

- Formally announced at CES 2012

- Tile-based deferred renderer

- Building on technology proven over 5 previous generations

- USC Universal Shading Cluster

- New scalar SIMD shader core

- General purpose compute is a first class citizen in the core ...

- ... while not forgetting what makes a shader core great for graphics

## **TBDR** *Tile-based*

#### Tile-based

- Split each render up into small tiles (32x32 for the most part)

- Bin geometry after vertex shading into those tiles

- Tile-based rasterisation and pixel shading

- Keep all data access for pixel shading on chip

#### Deferred rasterisation

- Don't actually get the GPU to do any pixel shading straight away

- HW support for fully deferred rasterisation and then pixel shading

- Rasterisation is pixel accurate

#### 6

#### Bandwidth savings across all phases of rendering

- Only fetch the geometry needed for the tile

- Only process the visible pixels in the tile

#### Efficient processing

End result

- Maximise available computational resources

- Do the best the hardware can with bandwidth

#### Maximising core efficiency

Lighting up the USC less often is always going to be a saving

### Minimising bandwidth

- Texturing less is a fantastic way to save power

- Geometry fetch and binning is often more than 10% of per-frame bandwidth

- Saves bandwidth for other parts of your render

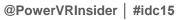

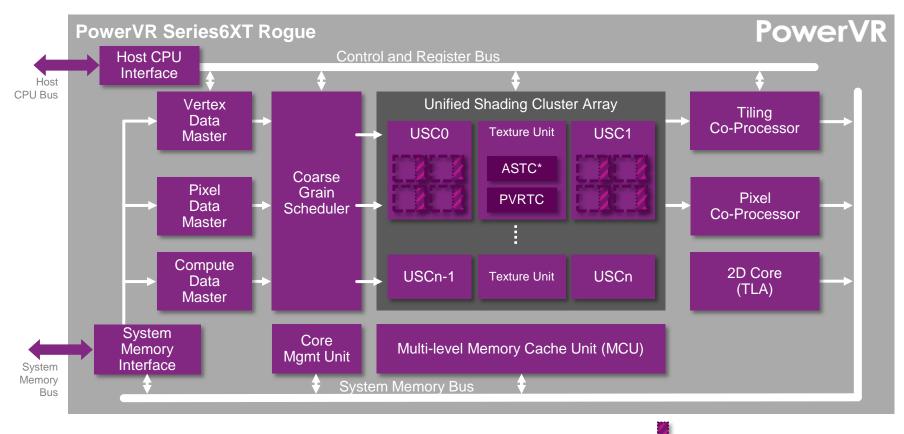

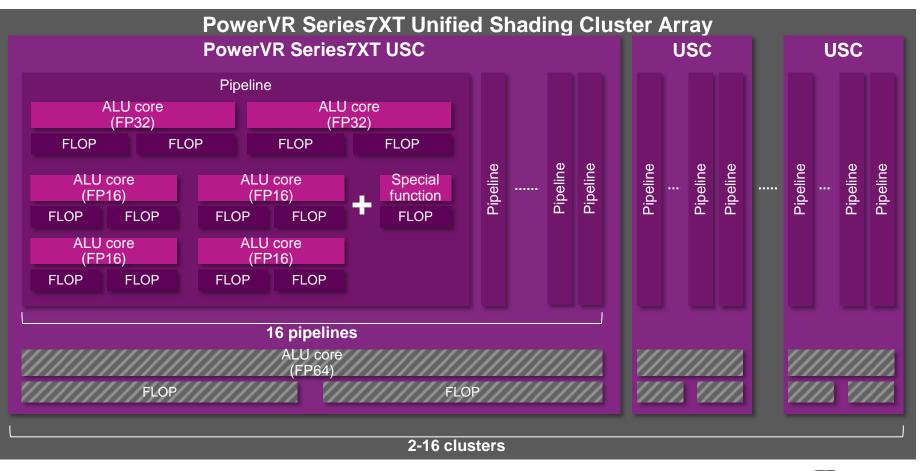

## Rogue USC Architectural Building Block

- Basic building block of the Rogue architecture

- Laid out in pairs, with a shared TPU

- 1, 0.5 and 0.25 USC designs are special

- Different balance in the design

- Tend to find their way into non-gaming applications

- 16-wide in hardware

- 32-wide branch granularity

- We run half a task/warp per clock

- Scalar SIMD

- Optimised ALU pipeline

- Mix of F32, F16, integer, floating point specials, logic ops

#### Configurable in the IP core

- F16 paths were sometimes optional, thankfully not any more

- F16 paths performance increased significantly after the first generation

#### Performance in your shader

- F32 paths are dual FMAD

- F16 paths can do different things per cycle depending on shader

- All up to the compiler

- ISA is available for you to interrogate though, with disassembling compilers

# **Rogue USC - Scalar**

- Hard to understate what a benefit this is

- Seems obvious to do, right?

- Vector architectures are just hard to program well

- Scalar isn't a free lunch

- Makes performance a lot more predictable for you

## **Rogue USC** *Programmable output registers*

- The pixel output registers in the ISA are read/write

- One per pixel

- Width depends on IP core

- We expose it programmatically with Pixel Local Storage

- Worked closely with ARM (thanks, Jan-Harald!)

- Doesn't matter that we hate their guts\*, still need to make life great for developers

## **Evolution**

Health Warning: Really Bad Diagrams<sup>™</sup>

# **Rogue Evolution**

- Architecture has changed quite a bit over time

- Rogue in 2010 still mostly looks like a Rogue today

- Significant evolutionary changes across the architecture

- Lots of it driven by developers before the IP is baked

- Lots of it driven by also analysing your stuff anyway

@PowerVRInsider | #idc15

Extra low power GFLOPS

Supports both LDR and HDR ASTC formats

# **Series6 to Series6XT**

Lots of lessons learned

- Improved scheduler

- Streamlined ISA

- Improved compute task efficiency

- Completely new F16 datapath

- Improved front-end for sustained geometry performance

- ASTC

Extra low power GFLOPS

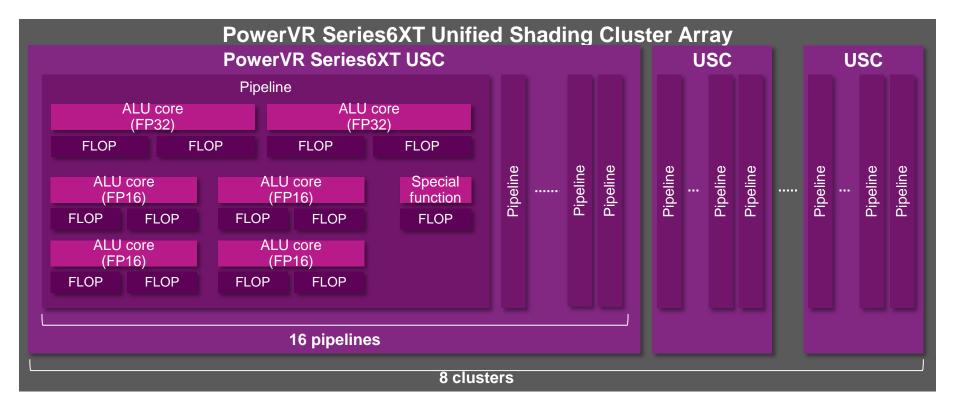

# **Series6XT to Series7XT**

Adding features and smoothing off rough edges

- Changed how the architecture scales

- Improved USC

- Streamlined ISA

- Features

- Hardware tessellation

- DX11-compliant USC (precision mainly)

- FP64

#### facebook.com/imgtec

#### : 🄰 @PowerVRInsider | #idc15

#### 22

## Into the future

- Exciting changes being worked on across the architecture

- USC

- Front-end

- Scaling

- Stuff you want!

- You can help

- We love feedback about the architecture and how it could best fit what you're doing

- Don't be shy

## Live Long, and Prosper

www.imgtec.com/idc